# 1

### Глава 7. СЕМЕЙСТВО МИКРОКОНТРОЛЛЕРОВ С8051F2xx

### 7.1. Обобщенная структура и состав семейства С8051F2xx

Семейство C8051F2xx состоит из 7 микроконтроллеров с номерами 206, 220, 221, 226, 230, 231 и 236[13]. Состав семейства и его основные характеристики приведены в таблице 7.1.

Таблица 7.1.

#### Состав семейства C8051F2xx

|           | MIPS (Peak) | Flash Memory | RAM, byte | SPI      | UART | WDT      | Timers (16 bit) | I/O Ports | ADC0 Resolution | ADC0 Inputs | Comparators | Package |

|-----------|-------------|--------------|-----------|----------|------|----------|-----------------|-----------|-----------------|-------------|-------------|---------|

| C8051F206 | 25          | 8k           | 1280      | 1        | V    | 1        | 3               | 32        | 12              | 32          | 2           | 48TQFP  |

| C8051F220 | 25          | 8k           | 256       | 1        | 1    | 1        | 3               | 32        | 8               | 32          | 2           | 48TQFP  |

| C8051F221 | 25          | 8k           | 256       | 1        | V    | 1        | 3               | 22        | 8               | 22          | 2           | 32LQFP  |

| C8051F226 | 25          | 8k           | 1280      | <b>V</b> | V    | V        | 3               | 32        | 8               | 32          | 2           | 48TQFP  |

| C8051F230 | 25          | 8k           | 256       | 1        | 1    | 1        | 3               | 32        | -               | -           | 2           | 48TQFP  |

| C8051F231 | 25          | 8k           | 256       | <b>V</b> | V    | <b>V</b> | 3               | 22        | -               | -           | 2           | 32LQFP  |

| C8051F236 | 25          | 8k           | 1280      | <b>V</b> | V    | V        | 3               | 32        | -               | -           | 2           | 48TQFP  |

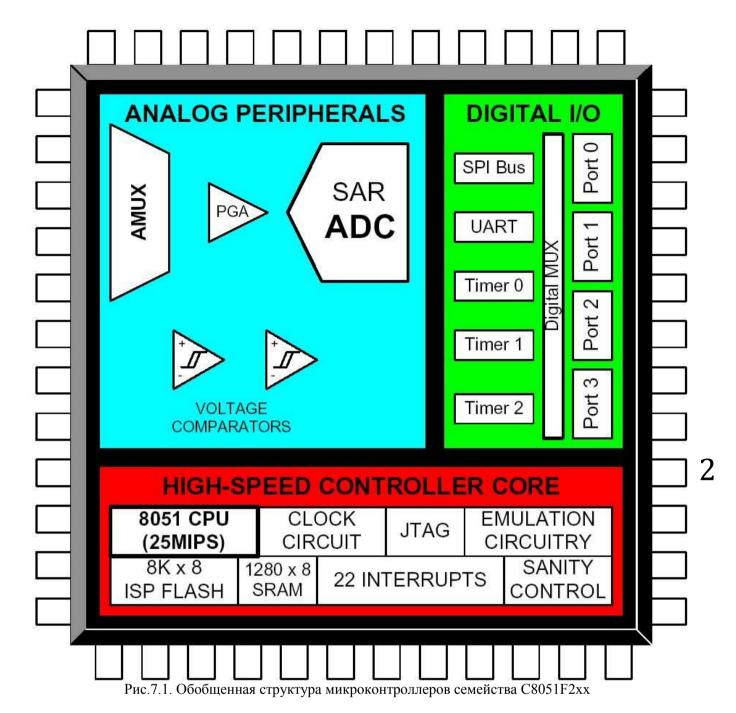

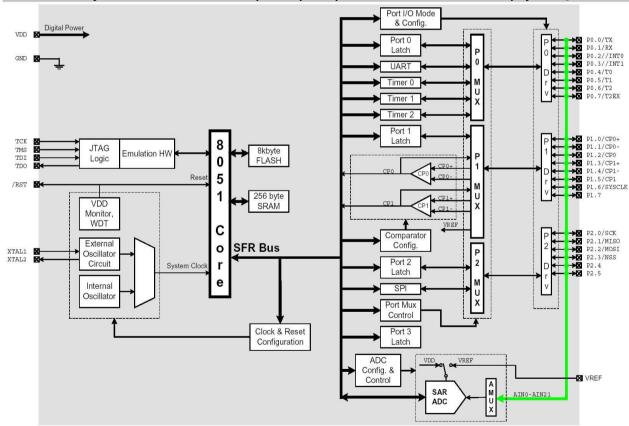

Обобщенная структура микроконтроллеров первого семейства C8051F2xx, представленная на рис.7.1, состоит из трех функциональных групп: аналоговой периферии (Analog Peripherals), цифровой периферии (Digital Peripherals) и высокопроизводительного контроллерного ядра (High-Speed Controller Core). Микроконтроллеры этого семейства значительно отличаются от предыдущих семейств.

Основными отличиями этого семейства от предыдущих являются:

- Значительно увеличенное количество входов мультиплексора аналого-цифрового преобразователя до 32:

- Аналого-цифровой преобразователь имеется только в 4 из 7 микроконтроллеров, причем только в одном C8051F206 он 12-битный, а в микроконтроллерах C8051F220/221/226 всего 8-битный;

- Отсутствие встроенных цифро-аналоговых преобразователей;

- Многие выводы портов ввода/вывода могут выполнять также функции фиксированных периферийных устройств. Кроме того, все порты ввода/вывода могут выполнять также роль аналоговых входов:

- Отсутствует коммутатор ресурсов Crossbar;

- Отсутствие программируемого массива-счетчика и интерфейса SMBus (I2C).

Как и в других семействах, в этом семействе имеется основной микроконтроллер - C8051F206, отличающийся от остальных наиболее полным набором периферии. Обобщенная структура микроконтроллеров семейства C8051F2xx приведена на рис.7.1.

Все микроконтроллеры семейства работают при напряжении питания от 2,7B до 3,6B в индустриальном диапазоне температур от -45 до +85С°. Линии портов ввода/вывода, сброса и JTAG работоспособны при питании 5B.

#### 7.2. Функциональные схемы, типы корпусов и назначение выводов

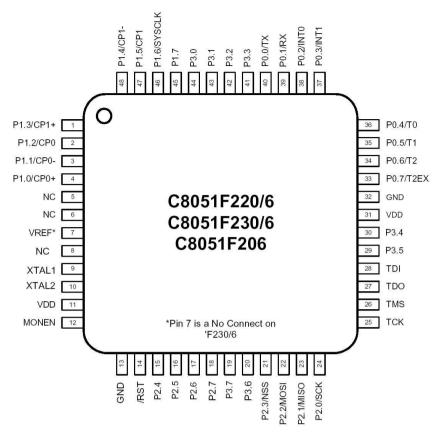

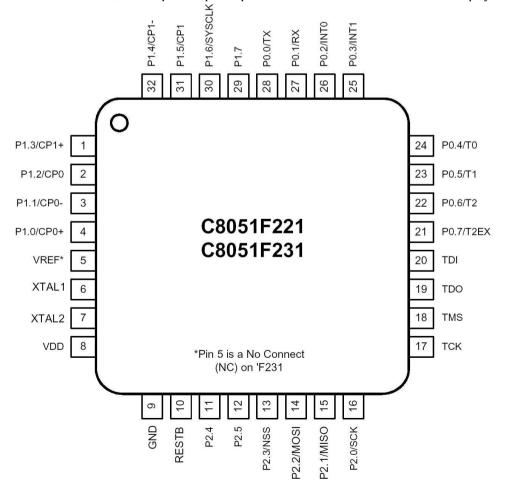

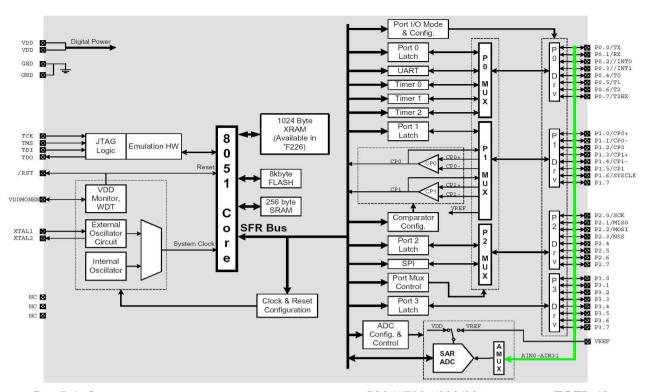

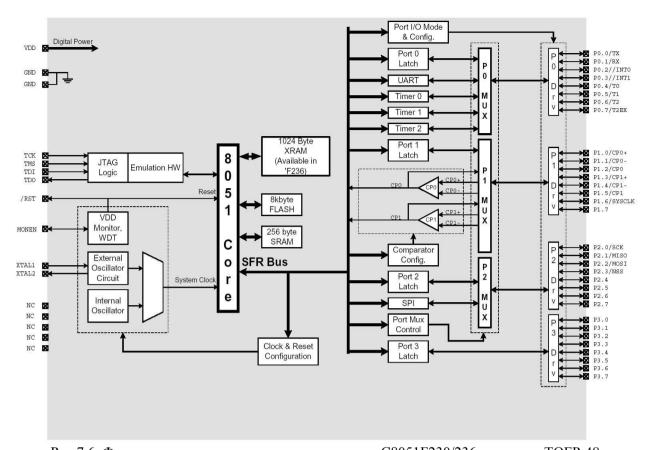

Микроконтроллеры семейства C8051F2xx производятся в двух типах корпусов. Микроконтроллеры C8051F206/220/226/230/236 выпускаются в корпусе с 48 выводами - TQFP-48 (см. рис.7.2). Микроконтроллеры C8051F221/231 выпускаются в корпусе с 32 выводами - LQFP-32 (см. рис.7.3). Функциональные схемы всех микроконтроллеров показаны на рис.7.4 - 7.7. Назначение выводов микроконтроллеров семейства C8051F2xx приведено в таблице 7.2.

Рис. 7.2. Расположение выводов микроконтроллеров C8051F206/220/226/230/236 в корпусе TQFP-48

Рис. 7.3. Расположение выводов микроконтроллеров C8051F221/231 в корпусе LQFP-32

Рис.7.4. Функциональная схема микроконтроллеров C8051F206/220/226 в корпусе TQFP-48

Рис. 7.5. Функциональная схема микроконтроллеров C8051F221 в корпусе LQFP-32

Рис. 7.6. Функциональная схема микроконтроллеров C8051F230/236 в корпусе TQFP-48 Port I/O Mode & Config. P0.0/TX

P0.1/RX

P0.1/RX

P0.2//INT0

P0.3//INT1

P0.4/T0

P0.5/T1

P0.6/T2

P0.7/T2EX VDD Port 0 Р Latch M U Timer 0 Timer 1 Timer 2 Port 1 P1.0/CP0+

→ P1.1/CP0→ P1.2/CP0

→ P1.3/CP1+

→ P1.4/CP1→ P1.5/CP1

→ P1.5/CP1

→ P1.5/SYSCLK Latch 8 JTAG TMS 8kbyte Emulation HW TDT Logic 0 FLASH 5 /RST M U X 256 byte SRAM VDD Monitor. WDT C Comparator External Config. SFR Bus 0 P 2 XTAL1 Oscillator XTAL2 Circuit Port 2 System Clock r Latch е M U X Internal SPI Oscillator Port Mux Control Clock & Reset Port 3 Configuration Latch NC X

Рис. 7.7. Функциональная схема микроконтроллеров C8051F231 в корпусе LQFP-32

Таблица 7.2.

Сводная таблица нумерации, названия и назначения выводов семейства С8051F2xx

|             |                    | ерации |                 | я и назначения выводов семейства C8051F2xx                                                                            |

|-------------|--------------------|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------|

| Имя         | Выводы             |        | Тип             | Описание                                                                                                              |

|             | 206,220,           | 221,   |                 |                                                                                                                       |

|             | 226,230,           | 231    |                 |                                                                                                                       |

|             | 236                |        |                 |                                                                                                                       |

| VDD         | 11, 31             | 8      |                 | Цифровое напряжение питания                                                                                           |

| GND         | 5, 6, 8,<br>13, 32 | 9      |                 | Цифровая земля. Выводы 5, 6 и 8 в корпусе TQFP-48 свободны, но их                                                     |

| MONEN       | 12                 |        | D In            | рекоменлуется соелинять с землей. Вход включения монитора питания (Только в корпусе TQFP-48). Разре-                  |

| TCK         | 25                 | 17     | D In            | шает работу монитора питания при подаче высокого уровня  JTAG Test Clock - тактовый сигнал с внутренней подтяжкой     |

| TMS         | 26                 | 18     | D In            | JTAG Test-Mode Select - сигнал режима с внутренней подтяжкой.                                                         |

| TDI         | 28                 | 20     | D In            | JTAG Test Data Input - сигнал входа данных с внутренней подтяжкой.                                                    |

|             |                    |        |                 | Запоминание данных происходит по переднему фронту ТСК импульсов.                                                      |

| TDO         | 27                 | 19     | D Out           | JTAG Test Data Output сигнал выхода данных с третьим состоянием.                                                      |

| XTAL1       | 9                  | 6      | A In            | Сдвиг данных происходит по заднему фронту ТСК импульсов. Вход кварцевого резонатора или внешнего генератора импульсов |

|             |                    |        |                 |                                                                                                                       |

| XTAL2       | 10                 | 7      | A Out           | Выход кварцевого резонатора.                                                                                          |

| RST/        | 14                 | 10     | D I/O           | Двунаправленный сигнал сброса.                                                                                        |

| VREF        | 7                  | 5      | A I/O           | Вход внешнего источника опорного напряжения для ADC. В микропроцессорах F230/231/236 вход не подсоединен              |

| CP0 +       | 4                  | 4      | A In            | Неинвертирующий вход аналогового компаратора 0                                                                        |

| CP0-        | 3                  | 3      | A In            | Инвертирующий вход аналогового компаратора 0                                                                          |

| CP0         | 2                  | 2      | D Out           | Выход аналогового компаратора 0                                                                                       |

| CP1 +       | 1                  | 1      | A In            | Неинвертирующий вход аналогового компаратора 1                                                                        |

| CP1-        | 48                 | 32     | A In            | Инвертирующий вход аналогового компаратора 1                                                                          |

| CP1         | 47                 | 31     | D Out           | Выход аналогового компаратора 1                                                                                       |

| P0.0/ TX    | 40                 | 28     | D I/O           | Бит 0 порта 0                                                                                                         |

| P0.1/RX     | 39                 | 27     | A In D I/O A In | Бит 1 порта 0                                                                                                         |

| P0.2/INT0   | 38                 | 26     | D I/O<br>A In   | Бит 2 порта 0                                                                                                         |

| P0.3/INT1   | 37                 | 25     | D I/O           | Бит 3 порта 0                                                                                                         |

| P0.4/T0     | 36                 | 24     | A In D I/O      | Бит 4 порта 0                                                                                                         |

| P0.5/T1     | 35                 | 23     | A In<br>D I/O   | Бит 5 порта 0                                                                                                         |

| P0.6/T2     | 34                 | 22     | A In<br>D I/O   | Бит 6 порта 0                                                                                                         |

| 1 0.0/12    | 34                 |        | A In            |                                                                                                                       |

| P0.7/T2EX   | 33                 | 21     | D I/O<br>A In   | Бит 7 порта 0                                                                                                         |

| P1.0/CP0+   | 4                  | 4      | D I/O<br>A In   | Бит 0 порта 1                                                                                                         |

| PI.I/CP0-   | 3                  | 3      | D I/O           | Бит 1 порта 1                                                                                                         |

| P1.2/CP0    | 2                  | 2      | A In            | Бит 2 порта 1                                                                                                         |

| P1.3/CP1+   | 1                  | 1      | A In D I/O      | Бит 3 порта 1                                                                                                         |

| P1.4/CP1-   | 48                 | 32     | A In<br>D I/O   | Бит 4 порта 1                                                                                                         |

| P1.5/CP1    | 47                 | 31     | A In<br>D I/O   | Бит 5 порта 1                                                                                                         |

| P1.6/SYSCLK | 46                 | 30     | A In<br>D I/O   | Бит 6 порта 1                                                                                                         |

| PI. 7       | 45                 | 29     | A In<br>D I/O   | Бит 7 порта 1                                                                                                         |

| D2 0/CCH    | 24                 | 1.0    | A In<br>D I/O   | Бит 0 порта 2                                                                                                         |

| P2.0/SCK    | 24                 | 16     | 1111/(1         | Тъмт и порта 7                                                                                                        |

Бит 1 порта 2

Бит 2 порта 2

Бит 3 порта 2

Бит 4 порта 2

Бит 5 порта 2

Бит 6 порта 2

Бит 7 порта 2

Бит 0 порта 3

Бит 1 порта 3

Бит 2 порта 3

Бит 3 порта 3

Бит 4 порта 3

Бит 5 порта 3

Бит 6 порта 3

Бит 7 порта 3

| $\overline{}$ |

|---------------|

|               |

|               |

# 7.3. Электрические параметры и предельные режимы эксплуатации

Общие электрические характеристики семейства приведены в таблице 7.3.

Таблица 7.3.

Общие электрические характеристики семейства C8051F2xx

P2.1/MISO

P2.2/MOSI

P2.3/NSS

P2.4

P2.5

P2.6

P2.7

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

23

22

21

15

16

17

18

44

43

42

41

30

29

20

19

15

14

13

11

12

D I/O

A In

D I/O

A In

D I/O

A In

D I/O A In

D I/O

A In

D I/O

A In

D I/O

A In D I/O

A In D I/O

A In D I/O

A In

D I/O

A In

D I/O

A In

D I/O

A In

D I/O A In

D I/O A In

| Параметр                            | Условия                         | MIN | HOPMA | MAX |

|-------------------------------------|---------------------------------|-----|-------|-----|

| Напряжение питания аналоговой час-  | Напряжение питания аналоговой   | 2.7 | 3.0   | 3.6 |

| ти, V                               | части должно быть больше 1V для |     |       |     |

|                                     | работы супервизора питания      |     |       |     |

| Ток потребления с активной аналого- | ADC и компараторы включены      |     | 9,5   |     |

| вой частью, mA                      | при тактовой частоте 25MHz      |     |       |     |

| Допустимая разница напряжений пи-   | VDD - VA+                       |     |       | 0.5 |

| тания аналоговой и цифровой частей, |                                 |     |       |     |

| V                                   |                                 |     |       |     |

| Напряжение питания цифровой части,  |                                 | 2.7 | 3.0   | 3.6 |

| V                                   |                                 |     |       |     |

| Ток потребления цифровой части в    | VDD = 2.7V, $Clock=25MHz$       |     | 9     |     |

| активном режиме, тА                 | VDD = 2.7V, $Clock=IMHz$        |     | 0.5   |     |

|                                     | VDD = 2.7V, $Clock = 32kHz$     |     | 10 μΑ |     |

| Ток потребления цифровой части в    | Генератор выключен              |     | 5     |     |

| пассивном режиме, µА                |                                 |     |       |     |

| Напряжения сохранения данных в      |                                 |     | 1.5   |     |

| RAM, V                              |                                 |     |       |     |

| Рабочий тепературный диапазон, °С   |                                 | -40 |       | +85 |

Предельные режимы эксплуатации приведены в таблице 7.4.

Таблица 7.4.

Предельные параметры семейства C8051F2xx

| предельные параметры семенеты сооз и 2км                                |                      |

|-------------------------------------------------------------------------|----------------------|

| Предельная температура корпуса                                          | -55 - 125°C          |

| Предельная температура хранения                                         | -65 - 150°C          |

| Предельные напряжения на всех выводах кроме VDD и Port I/O по отношению | -0.3V - (VDD + 0.3V) |

| к DGND                                                               |              |

|----------------------------------------------------------------------|--------------|

| Предельные напряжения на всех выводах Port I/O и RST/ по отношению к | -0.3V - 5.8V |

| DGND                                                                 |              |

| Предельное напряжение на вывода VDD по отношению к DGND              | -0.3V - 4.2V |

| Максимальный общий ток через VDD, AV+, DGND и AGND                   | 800mA        |

| Максимальный выходной ток через любой вывода Port I/O                | 100mA        |

| Максимальный выходной ток через любой другой вывод                   | 25mA         |

Превышение параметров, указанных в таблице, может привести к повреждению изделия. Не рекомендуется эксплуатация изделия в предельных режимах, т.к. это приводит к снижению надежности и ресурса.

#### 7.4. Подсистемы семейства C8051F2xx

Микроконтроллеры семейства C8051F2xx имеют типовое ядро CIP-51 фирмы Cygnal с подсистемой отладки и программирования JTAG и набором инструкций, описанные в разделах 2.1-2.3. Особенностями ядра данного семейства является наличие у всех микроконтроллеров семейства трех шестнадцатиразрядных таймеров/счетчиков и различное количество портов ввода/вывода у микроконтроллеров, выполненных в различных корпусах.

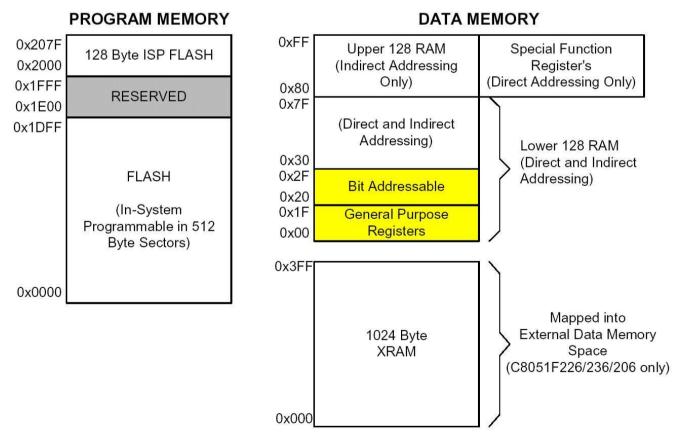

Ядро оснащено встроенной памятью данных с произвольным доступом (RAM) объемом 256 байт (0x00-0xFF).

Младшие 128 байт (0x00-0x7F) доступны инструкциям с прямой и косвенной адресацией, регистры специальных функций SFR доступны только инструкциям с прямой адресацией, а старшие 128 байт (0x80-0xFF) - только инструкциям с косвенной адресацией. Первые 32 байта (0x00-0x1F) адресуются как четыре банка регистров общего назначения, а следующие 16 байт (0x20-0x2F) - имеют битовую адресацию.

Кроме этого, микроконтроллеры C8051F226/236/206 дополнительно имеют 1024 байта оперативной памяти во внешнем адресном пространстве памяти данных. Этот 1К блок может быть доступен с помощью инструкции MOVX. Карта памяти семейства микроконтроллеров C8051F2xx показана на рис.7.8.

Рис. 7.8. Карта памяти семейства C8051F2xx

#### 7.5. Подсистема регистров специальных функций SFR

Прямо адресуемое адресное пространство памяти данных 0x80-0xFF в стандартном 8051 микро-контроллере занято регистрами специальных функций (SFRs). С помощью этих регистров осуществляется управление и обмен данными между ресурсами ядра СIP-51 и периферией. Регистры специальных функций ядра СIP-51 с одной стороны соответствуют регистрам стандартного 8051, а с другой - дополнены возможностями конфигурирования и обмена данными с оригинальными подсистемами микроконтроллеров Суgnal.

Поскольку описываемое семейство имеет "облегченный" набор периферийных устройств, оно, соответственно, имеет одностраничное SFR пространство адресов с небольшой насыщенностью (по сравнению со всеми предыдущими семействами). Карта адресов регистров специальных функций семейства C8051F2xx приведена в таблице 7.5.

Таблица 7.5.

Таблица 7.6.

Карта адресов регистров специальных функций SFR семейства C8051F2xx

| F8 | SPI0CN              |        |         |                     |                      |                      |                      | WDTCN                |

|----|---------------------|--------|---------|---------------------|----------------------|----------------------|----------------------|----------------------|

| F0 | В                   | P0MODE | PI MODE | P2MODE              | P3MODE <sup>2</sup>  |                      | EIP1                 | EIP2                 |

| E8 | ADC0CN <sup>1</sup> |        |         |                     |                      |                      |                      | RSTSRC               |

| E0 | ACC                 | PRT0MX | PRT1MX  | PRT2MX              |                      |                      | EIE1                 | EIE2                 |

| D8 |                     |        |         |                     |                      |                      |                      |                      |

| D0 | PSW                 | REF0CN |         |                     |                      |                      |                      |                      |

| C8 | T2C0N               |        | RCAP2L  | RCAP2H              | TL2                  | TH2                  |                      |                      |

| C0 |                     |        |         |                     | ADC0GTL <sup>4</sup> | ADC0GTH <sup>1</sup> | ADC0LTL <sup>4</sup> | ADC0LTH <sup>1</sup> |

| B8 | IP                  |        |         | AMX0SL <sup>1</sup> | ADC0CF <sup>1</sup>  |                      | ADC0L <sup>4</sup>   | ADC0H <sup>1</sup>   |

| B0 | P3                  | OSCXCN | OSCICN  |                     |                      |                      | FLSCL                | FLACL                |

| A8 | IE                  |        |         |                     |                      | PRT1IF               |                      | EMI0CN <sup>3</sup>  |

| A0 | P2                  |        |         |                     | PRT0CF               | PRT1CF               | PRT2CF               | PRT3CF               |

| 98 | SCON                | SBUF   | SPI0CFG | SPI0DAT             |                      | SPI0CKR              | CPT0CN               | CPT1CN               |

| 90 | PI                  |        |         |                     |                      |                      |                      |                      |

| 88 | TCON                | TMOD   | TL0     | TL1                 | TH0                  | TH1                  | CKCON                | PSCTL                |

| 80 | P0                  | SP     | DPL     | DPH                 |                      |                      |                      | PCON                 |

|    | 0(8)                | 1(9)   | 2(A)    | 3(B)                | 4(C)                 | 5(D)                 | 6(E)                 | 7(F)                 |

- 1. Микроконтроллеры C8051F230/231/236 не содержат этих регистров.

- 2. Микроконтроллеры C8051F221/231 не содержат этих регистров.

- 3. Только для микроконтроллеров С8051F206/226/236.

- 4. Только для микроконтроллеров C8051F206.

В таблице 7.6. регистры приведены в алфавитном порядке. Пропущенные адреса зарезервированы.

Таблица адресов регистров специальных функций в алфавитном порядке

Название ре-Адрес Описание функционального назначения регистра Раздел гистра регистра описания ACC 0xE0 3.6.24 Аккумулятор ADC0CF 0xBC Конфигурация ADC0 3.6.3 ADC0CN 0xE8 Управление ADC 0 3.6.4 ADC0GTH 0xC5 Старший байт верхнего порога данных АОСО 3.6.7 ADC0GTL 0xC4 Младший байт верхнего порога данных ADC0 3.6.8 ADC0H 0xBF Старший байт данных ADC0 3.6.5 ADC0L 0xBE Младший байт данных ADC0 3.6.6 ADC0LTH 0xC7 Старший байт нижнего порога данных ADC0 3.6.9 ADC0LTL 0xCE 3.6.10 Младший байт нижнего порога данных ADC0 AMX0SL 0xBB Выбор каналов мультиплексора MUX ADC0 7.6.2

| В       | 0xFO         | Регистр В                                                     | 3.6.25 |

|---------|--------------|---------------------------------------------------------------|--------|

| CKCON   | 0xFO<br>0x8E | Регистр управления тактовой частотой таймеров                 | 3.6.67 |

| CPT0CN  | 0x9E         | Управление компаратором 0                                     | 3.6.17 |

| CPTICN  | 0x9E<br>0x9F | Управление компаратором 0  Управление компаратором 1          | 3.6.18 |

| DPH     | 0x9F<br>0x83 | у правление компаратором 1 Старший байт указателя данных      | 3.6.22 |

|         |              |                                                               |        |

| DPL     | 0x82         | Младший байт указателя данных                                 | 3.6.21 |

| EIE1    | 0xE6         | Разрешение дополнительных прерываний 1                        | 3.6.29 |

| EIE2    | 0xE7         | Разрешение дополнительных прерываний 2                        | 3.6.30 |

| EIP1    | 0xF6         | Приоритеты дополнительных прерываний 1                        | 3.6.31 |

| EIP2    | 0xF7         | Приоритеты дополнительных прерываний 2                        | 3.6.32 |

| EMI0CN  | 0xAF         | Управление интерфейсом внешней памяти                         | 7.6.8  |

| FLACL   | 0xB7         | Ограничение доступа Flash                                     | 7.6.7  |

| FLSCL   | 0xB6         | Управление временем доступа к Flash                           | 3.6.36 |

| IE      | 0xA8         | Разрешение прерываний                                         | 3.6.27 |

| IP      | 0xB8         | Управление приоритетами прерываний                            | 3.6.28 |

| OSCICN  | 0xB2         | Управление внутренним генератором                             | 3.6.40 |

| OSCXCN  | 0xB1         | Управление внешним генератором                                | 7.6.10 |

| P0      | 0x80         | Выходной регистр Port 0                                       | 3.6.45 |

| P1      | 0x90         | Выходной регистр Port 1                                       | 3.6.47 |

| P2      | 0xA0         | Выходной регистр Port 2                                       | 3.6.50 |

| P3      | 0xB0         | Выходной регистр Port 3                                       | 3.6.52 |

| P0MODE  | 0xF1         | Регистр цифрового/аналогового режима порта 0                  | 7.6.15 |

| P1MODE  | 0xF2         | Регистр цифрового/аналогового режима порта 1                  | 7.6.15 |

| P2MODE  | 0xF3         | Регистр цифрового/аналогового режима порта 2                  | 7.6.15 |

| P3MODE  | 0xF4         | Регистр цифрового/аналогового режима порта 3                  | 7.6.15 |

| PCON    | 0x87         | Управление питанием                                           | 3.6.33 |

| PSCTL   | 0x8F         | Управление R/W к памяти программ                              | 3.6.34 |

| PRT0CF  | 0xA4         | Конфигурация порта 0                                          | 3.6.46 |

| PRT1CF  | 0xA5         | Конфигурация порта 1                                          | 3.6.48 |

| PRT1IF  | 0xAD         | Регистр флагов прерывания порта 1                             | 3.6.49 |

| PRT2CF  | 0xA6         | Конфигурация порта 2                                          | 3.6.51 |

| PRT3CF  | 0xA7         | Конфигурация порта 3                                          | 3.6.53 |

| PRT0MX  | 0xE1         | Регистр мультиплексора порта 0                                | 7.6.12 |

| PRT1MX  | 0xE2         | Регистр мультиплексора порта 1                                | 7.6.13 |

| PRT2MX  | 0xE3         | Регистр мультиплексора порта 2                                | 7.6.14 |

| PSW     | 0xD0         | Слово состояния программы                                     | 3.6.23 |

| RCAP2H  | 0xCB         | Старший байт таймера/счетчика 2                               | 3.6.74 |

| RCAP2L  | 0xCA         | Младший байт таймера/счетчика 2                               | 3.6.73 |

| REF0CN  | 0xDl         | Управление источником опорного напряжения                     | 7.6.4  |

| RSTSRC  | 0xEF         | Управление источниками сброса                                 | 7.6.9  |

| SBUF0   | 0x99         | Буфер данных последовательного порта 0 (UART0)                | 3.6.63 |

| SCON0   | 0x98         | Управление последовательным портом 0 (UART0)                  | 3.6.64 |

| SP      | 0x81         | Указатель стека                                               | 3.6.20 |

| SPI0CFG | 0x9A         | Конфигурация последовательного периферийного интерфейса (SPI) | 3.6.59 |

| SPI0CKR | 0x9D         | Управление скоростью SPI                                      | 3.6.61 |

| SPI0CN  | 0xF8         | Управление шиной SPI                                          | 3.6.60 |

| SPI0DAT | 0x9B         | Данные SPI                                                    | 3.6.62 |

| T2CON   | 0xC8         | Управление таймерами/счетчиками 2                             | 3.6.72 |

|         |              | A                                                             |        |

| 1 | 1 |

|---|---|

| T | Τ |

| TCON  | 0x88 | Управление таймерами/счетчиками        | 3.6.65 |

|-------|------|----------------------------------------|--------|

| TH0   | 0x8C | Старший байт данных таймера/счетчика 0 | 3.6.70 |

| TH1   | 0x8D | Старший байт данных таймера/счетчика 1 | 3.6.71 |

| TH2   | 0xCD | Старший байт данных таймера/счетчика 2 | 3.6.76 |

| TL0   | 0x8A | Младший байт данных таймера/счетчика 0 | 3.6.68 |

| TL1   | 0x8B | Младший байт данных таймера/счетчика 1 | 3.6.69 |

| TL2   | 0xCC | Младший байт данных таймера/счетчика 2 | 3.6.75 |

| TMOD  | 0x89 | Режимы таймеров счетчиков              | 3.6.66 |

| WDTCN | 0xFF | Управление охранным счетчиком (WDT)    | 3.6.38 |

#### 7.6. Регистры SFR

Управление и обмен данными с всей аналоговой и цифровой периферией микроконтроллеры семейства C8051F2xx осуществляют через регистры SFR. Для регистров, описание которых полностью совпадает с описанием регистров других семейств, даются ссылки на соответствующие разделы в таблице 7.6. Для остальных регистров ниже будет приведено подробное описание. Кроме того, в этом разделе будут даны описания некоторых функциональных узлов, отличающихся от приведенных в главе 2 или отсутствующих в ней.

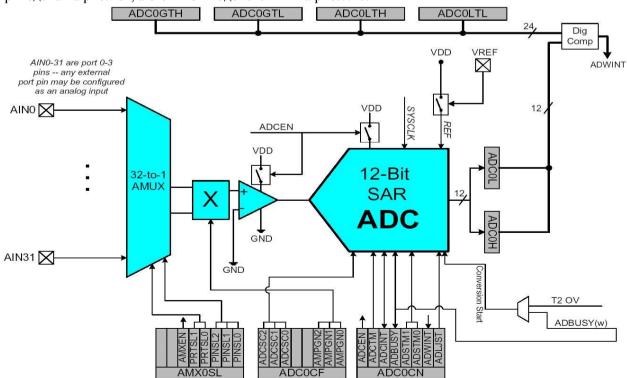

## 7.6.1. Аналого-цифровые преобразователи семейства C8051F2xx

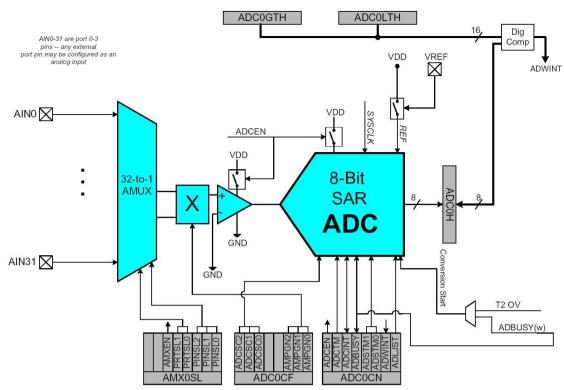

Как уже отмечалось выше, четыре (из семи) микроконтроллеров семейства C8051F2xx оснащены аналого-цифровыми преобразователями, причем микроконтроллер C8051F206 оснащен 12-битным преобразователем, а микроконтроллеры C8051F220/221/226 - 8-битными. Сами аналого-цифровые преобразователи семейства C8051F 2xx функционально не отличаются от используемых в предыдущих семействах. Основное отличие аналого-цифровой подсистемы семейства заключается в наличии развитого 32-канального аналогового мультиплексора, который обладает возможностью коммутации входов на все выводы портов микроконтроллера. Функциональная схема 12-битной подсистемы ADC приведена на рис.7.9., а 8-битной подсистемы - на рис.7.10.

Рис. 7.9. Функциональная схема 12-битной подсистемы ADC

Рис. 7.10. Функциональная схема 8-битной подсистемы ADC

7.6.2.AMX0SL - Регистр выбора каналов мультиплексора (C8051F206/220/221/226)

| Название регистра: AMX0SL |       |       |          | MUX0 Cha | nnel Select R | egister      |        |                  |   |

|---------------------------|-------|-------|----------|----------|---------------|--------------|--------|------------------|---|

| SFR адрес / страница:     |       |       | 0xBB / 0 |          | Значение п    | осле сброса: | 000000 | 00000000b (0x00) |   |

|                           | _     |       |          |          |               |              |        |                  |   |

|                           | R/W   | R/W   | R/W      | R/W      | R/W           | R/W          | R/W    | R/W              |   |

|                           | -     | -     | AMXEN    | PRTSL1   | PRTSL0        | PINSL2       | PINSL1 | PINSL0           | 1 |

|                           | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3         | Bit 2        | Bit 1  | Bit 0            | - |

Биты 7-6 не используются, при чтении возвращают 00b, при записи значение игнорируются.

Бит 5: AMXEN - AMUX Enable - бит разрешения (1) аналогового мультиплексора;

Битѕ 4-3: PRTSL1-0 - Port Select Bits - биты выбора порта:

- 00 Порт 0 выбран для конфигурации выводов в качестве аналоговых входов;

- 01 Порт 1 выбран для конфигурации выводов в качестве аналоговых входов;

- 10 Порт 2 выбран для конфигурации выводов в качестве аналоговых входов;

- 11 Порт 3 выбран для конфигурации выводов в качестве аналоговых входов;

Биты 2-0: PINSL2-0 - Pin Select Bits - биты выбора выводов:

- 000 Вывод 0 выбранного порта будет использоваться в качестве аналогового входа;

- 001 Вывод 1 выбранного порта будет использоваться в качестве аналогового входа;

- 010 Вывод 2 выбранного порта будет использоваться в качестве аналогового входа;

- 011 Вывод 3 выбранного порта будет использоваться в качестве аналогового входа;

- 100 Вывод 4 выбранного порта будет использоваться в качестве аналогового входа;

- 101 Вывод 5 выбранного порта будет использоваться в качестве аналогового входа;

- 110 Вывод 6 выбранного порта будет использоваться в качестве аналогового входа;

- 111 Вывод 7 выбранного порта будет использоваться в качестве аналогового входа.

Следует отметить, что выбор порта битами PRTSL1-0 не означает, что все выводы этого порта будут использоваться в качестве аналоговых входов. После выбора собственно порта необходимо задать биты PINSL2-0 для выбора вывода порта, который будет использоваться в качестве аналогового входа.

#### 7.6.3. Источник опорного напряжения в микроконтроллерах С8051A206/220/221/226

В микроконтроллерах описываемого семейства, содержащих аналого-цифровой преобразователь, отсутствует встроенный источник опорного напряжения, поэтому необходимо либо использовать внешний источник опорного напряжения, подсоединив его ко входу VREF, либо в качестве опорного напряжения использовать напряжение питания, задав соответствующие биты регистра REF0CN[1:0].

7.6.4. REF0CN - Регистр выбора источника опорного напряжения

| Название регистра: REF0CN - Reference Control Register |       |       |          |       |            |             |           |                  |   |

|--------------------------------------------------------|-------|-------|----------|-------|------------|-------------|-----------|------------------|---|

| SFR адрес / страница:                                  |       |       | 0xD1 / 0 |       | Значение п | осле сброса | : 0000000 | 00000000b (0x00) |   |

|                                                        |       |       |          |       |            |             |           |                  |   |

|                                                        | R/W   | R/W   | R/W      | R/W   | R/W        | R/W         | R/W       | R/W              |   |

|                                                        | -     | -     | -        | -     | -          | -           | REFSL1    | REFSL0           |   |

|                                                        | Bit 7 | Bit 6 | Bit 5    | Bit 4 | Bit 3      | Bit 2       | Bit 1     | Bit 0            | _ |

Биты 7-2 не используются, читаются как 00000b, при записи значение игнорируется;

Биты 1-0: REFSL1-0 - Voltage reference selection - выбор источника опорного напряжения:

- 00 внешний источник с вывода VREF;

- 01 резерв;

- 10 резерв;

- 11 в качестве опорного используется напряжение питания VDD (внутреннее соединение!!!).

#### 7.6.5. Источники прерываний

Ядро CIP-51 семейства микроконтроллеров имеет развитый обработчик прерываний, обслуживающий 22 вектора прерывания, приведенные в таблице 7.7.

Источники прерываний ядра CIP-51семейства F8051F2xx

**Таблица** 7.7 **2**

| Источник прерываний          | Вектор | Приоритет | Флаг прерывания         | Разрешено       |

|------------------------------|--------|-----------|-------------------------|-----------------|

| Reset                        | 0x0000 | Высший    | Нет                     | Всегда разрешен |

| External Interrupt 0 (INT0/) | 0x0003 | 0         | IE0 (TCON.1)            | EX0 (IE.0)      |

| Timer 0 Overflow             | 0x000B | 1         | TF0 (TCON.5)            | ET0 (IE.1)      |

| External Interrupt 1 (INT1/) | 0x0013 | 2         | IE1 (TCON.3)            | EX1 (IE.2)      |

| Timer 1 Overflow             | 0x001B | 3         | TF1 (TCON.7)            | ET1 (IE.3)      |

| Serial Port (UART)           | 0x0023 | 4         | RI (SCON.0) TI (SCON.1) | ES (IE.4)       |

| Timer 2 Overflow (или EXF2)  | 0x002B | 5         | TF2 (T2CON.7)           | ET2 (IE.5)      |

| Serial Peripheral Interface  | 0x0033 | 6         | SPIF (SPIOCN.7)         | ESPI0 (EIE1.0)  |

| ADC0 Window Comparison       | 0x0043 | 8         | ADWINT (ADC0CN.2)       | EWADC0 (EIE1.2) |

| Comparator 0 Falling Edge    | 0x0053 | 10        | CP0FIF (CPT0CN.4)       | ECP0F (EIE1.4)  |

| Comparator 0 Rising Edge     | 0x005B | 11        | CP0RIF (CPT0CN.5)       | ECPOR (EIE1.5)  |

| Comparator 1 Falling Edge    | 0x0063 | 12        | CP1FIF (CPT1CN.4)       | ECP1F (EIE1.6)  |

| Comparator 1 Rising Edge     | 0x006B | 13        | CP1RIF (CPT1CN.5)       | ECP1R (EIE1.7)  |

| ADC0 End of Conversion       | 0x007B | 15        | ADCINT (ADC0CN.5)       | EADC0 (EIE2.1)  |

| External Interrupt 4         | 0x0083 | 16        | IE4 (PRT1IF.4)          | EX4 (EIE2.2)    |

| External Interrupt 5         | 0x008B | 17        | IE5 (PRT1IF.5)          | EX5 (EIE2.3)    |

| External Interrupt 6         | 0x0093 | 18        | IE6 (PRT1IF.6)          | EX6 (EIE2.4)    |

| External Interrupt 7         | 0x009B | 19        | IE7 (PRT1IF.7)          | EX7 (EIE2.5)    |

| Unused Interrupt Location    | 0x00A3 | 20        | Нет                     | Резерв (EIE2.6) |

| External Crystal OSC Ready   | 0x00AB | 21        | XTLVLD (OSCXCN.7)       | EXVLD (EIE2.7)  |

#### 7.6.6. Система секретности

Система секретности микроконтроллеров семейства С8051F2xx значительно отличается от принятой у стандартного 8051.

Программная память условно разделена на несколько областей. Память с адресами от 0х0000 до 0x1DFD разделена на 8 фрагментов размером по 1 килобайту, каждый из которых может быть защищен как от чтения, так и от записи/стирания. Кроме того, существует два байта секретности, расположенные по адресам 0x1DFE и 0x1DFF. По адресу 0x1DFE расположен байт защиты памяти программ от записи/стирания через JTAG интерфейс. По адресу 0x1DFF расположен байт защиты памяти программ от чтения через JTAG интерфейс. Обнуление каждого их битов в этих двух байтах запрещает соответствующее действие в определенном фрагменте памяти, как показано в таблице 7.8.

Таблица 7.8

Таблица битов секретности

| Бит         | Запрещаемый фрагмент памяти |

|-------------|-----------------------------|

| 7 (старший) | 0x1C00 - 0x1DFD             |

| 6           | 0x1800 - 0x1BFF             |

| 5           | 0x1400 - 0x17FF             |

| 4           | 0x1000 - 0x13FF             |

| 3           | 0x0C00 - 0x0FFF             |

| 2           | 0x0800 - 0x0BFF             |

| 1           | 0x0400 - 0x07FF             |

| 0           | 0x0000 - 0x03FF             |

Область памяти, содержащая байты секретности, может быть записана программно, но не может быть программно стерта. Обращение при операции JTAG стирания к любому из байтов секретности приведет к полному стиранию программы, за исключением зарезервированной области. Полное стирание возможно только через JTAG. Если при операции JTAG стирания к любому из обычных байтов в области 0x1C00 - 0x1DFF (не байтов секретности) произойдет обращение, это приведет к стиранию только указанной области, включая и байты секретности.

Кроме этого, в адресном пространстве памяти имеется еще область с адресами 0x2000 - 0x207F, которая запирается только в случае, если заперты все 8 младших блока.

7.6.7. FLACL - Регистр ограничения доступа к Flash памяти

| Название регистра: |       |       | FLACL -Flas | FLACL -Flash Access Limit |              |                  |       |       |  |  |

|--------------------|-------|-------|-------------|---------------------------|--------------|------------------|-------|-------|--|--|

| SFR адрес:         |       | 0xB7  |             | Значение п                | юсле сброса: | 00000000b (0x00) |       |       |  |  |

|                    | R/W   | R/W   | R/W         | R/W                       | R/W          | R/W              | R/W   | R/W   |  |  |

|                    | Bit 7 | Bit 6 | Bit 5       | Bit 4                     | Bit 3        | Bit 2            | Bit 1 | Bit 0 |  |  |

В регистр FLACL записывается старший байт 16-битного адреса, ниже которого память программ не может быть прочитана инструкциями MOVX и MOVC. Попытка чтения возвращает 0 значение. Этот регистр доступен для записи только один раз после сброса. Остальные попытки записи игнорируются до следующего сброса.

7.6.8. EMI0CN - Регистр управления внешней памятью

| Ha         | звание регис | стра: | EMIOCN - External Memory Interface Control |       |            |             |           |                  |   |

|------------|--------------|-------|--------------------------------------------|-------|------------|-------------|-----------|------------------|---|

| SFR адрес: |              |       | 0xAF                                       |       | Значение п | осле сброса | : 0000000 | 00000000b (0x00) |   |

|            |              |       |                                            |       |            |             |           |                  |   |

|            | R            | R     | R                                          | R     | R          | R/W         | R/W       | R/W              |   |

|            | -            | -     | -                                          | -     | -          | -           | PGSEL1    | PGSEL0           |   |

|            | Bit 7        | Bit 6 | Bit 5                                      | Bit 4 | Bit 3      | Bit 2       | Bit 1     | Bit 0            | - |

Биты 7-2 не используются, при чтении возвращают 000000b.

Биты 1-0: PGSEL1-0 - XRAM Page Select Bits - биты выбора страницы. Биты выбирают страницу памяти при использовании 8-битной команды MOVX:

00 - 0x000 - 0x0FF;

01 - 0x100 - 0x1FF;

10 - 0x200 - 0x2FF;

11 - 0x300 - 0x3FF.

| 7.6.9. | RSTSRC | <u>- ]</u> | Регистр | ист | гочн | иков | сброса |

|--------|--------|------------|---------|-----|------|------|--------|

|        |        |            | _ ~_~   | ~   | _    | ~    |        |

| Ha         | звание регис | стра: | RSTSRC - Reset Source Register |            |              |        |         |        |   |

|------------|--------------|-------|--------------------------------|------------|--------------|--------|---------|--------|---|

| SFR адрес: |              | 0xEF  |                                | Значение п | осле сброса: | XXXXXX | xxxxxxx |        |   |

|            | _            |       |                                |            |              |        |         |        |   |

|            | R            | R     | R/W                            | R/W        | R            | R      | R/W     | R      |   |

|            | -            | -     | C0RSEF                         | SWRSEF     | WDTRST       | MCDREF | PORSF   | PINRSF |   |

|            | Bit 7        | Bit 6 | Bit 5                          | Bit 4      | Bit 3        | Bit 2  | Bit 1   | Bit 0  | - |

ВНИМАНИЕ! К этому регистру не применимы операции чтения-модификации-записи!!!

Биты 7-6 -зарезервированы;

- Бит 5: CORSEF Comparator 0 Reset Enable and Flag бит разрешения и флаг сброса от компаратора 0. При записи: 1 разрешает (0 - запрещает) использование компаратора 0 в качестве источника сброса при низком логическом уровне на выходе. При чтении: логическая 1 означает, что предыдущий сброс произошел от компаратора 0, соответственно, логический 0 означает, что сброс произошел от другого источника.

- Бит 4: SWRSF Software Reset Force and Flag бит / флаг программного сброса. При записи 1 отключается внешний вход сброса RST/. При чтении: 1 означает, что сброс произошел от записи в SWRSF

- Бит 3: WDTRSF Watchdog Timer Reset Flag флаг сброса охранного таймера. Логическая 1 означает, что предыдущий сброс произошел от WDT.

- Бит 2: MCDRST Missing Clock Detector Flag флаг отсутствия тактирования. Логическая 1 при чтении означает, что предыдущий сброс произошел от отсутствия тактовой частоты.

- Бит 1: PORSF Power-On Reset Force and Flag флаг сброса после включения питания. Логическая 1 при чтении означает, что предыдущий сброс произошел после включения питания. Запись 1 вызывает сброс и переводит вход RST/ в низкий логический уровень, чтение 1 означает что предыдущий 5 сброс произошел после включения питания.

- Бит 0: PINRSF HW Pin Reset Flag -флаг вывода RST/. При чтении 1 означает, что последний сброс произошел от вывода RST/.

7.6.10. OSCXCN - Регистр управления внешним тактовым генератором

| Ha                    | звание регис | стра:   | OSCXCN - E | OSCXCN - External Oscillator Control Register |              |         |                  |       |   |

|-----------------------|--------------|---------|------------|-----------------------------------------------|--------------|---------|------------------|-------|---|

| SFR адрес / страница: |              | 0xB1    |            | Значение п                                    | осле сброса: | 0011000 | 00110000b (0x00) |       |   |

|                       | _            |         | _          |                                               | _            |         |                  |       |   |

|                       | R/W          | R/W     | R/W        | R/W                                           | R/W          | R/W     | R/W              | R/W   |   |

|                       | XTLVLD       | XOSCMD2 | XOSCMD1    | XOSCMD0                                       | -            | XFCN2   | XFCN1            | XFCN0 |   |

|                       | Bit 7        | Bit 6   | Bit 5      | Bit 4                                         | Bit 3        | Bit 2   | Bit 1            | Bit 0 | 1 |

- Бит 7: XTLVLD Cristal Oscillator Valid Flag флаг готовности кварцевого генератора (только если XOSCMD=1xx). При выходе генератора на нормальный режим устанавливается логическая 1.

- Биты 6-4: XOSCMD2-0 External Oscillator Mode Bits биты установки режима внутреннего генератора:

- 00x- выключен;

- 010 - внешний генератор, подключенный на вывод XLAT1;

- 011 - внешний генератор, подключенный на вывод XLAT1 с делением на 2;

- 10x - RC/C генератор с делением на 2;

- 110 - кварцевый резонатор;

- 111 - кварцевый резонатор с делением на 2.

- Бит 3: зарезервирован.

- Биты 2-0: XFCN External Oscillator Frequency Control Bits код установки частоты в соответствии с таблицей 7.9.

16

Коды установки частоты

| XFCN | Кварцевый резонатор (XOSCMD=llx)                                                                      | RC цепочка (XOSCMD=10x)                                  | Конденсатор С<br>(XOSCMD=10x) |

|------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|

| 000  | f < 32kHz                                                                                             | f< 25kHz                                                 | K Factor = 0.44               |

| 001  | 32 kHz <f< 84="" khz<="" td=""><td>25kHz <f< 50khz<="" td=""><td>K Factor =1.4</td></f<></td></f<>    | 25kHz <f< 50khz<="" td=""><td>K Factor =1.4</td></f<>    | K Factor =1.4                 |

| 010  | 84 kHz <f< 225="" khz<="" td=""><td>50kHz <f< 100khz<="" td=""><td>K Factor = 4.4</td></f<></td></f<> | 50kHz <f< 100khz<="" td=""><td>K Factor = 4.4</td></f<>  | K Factor = 4.4                |

| 011  | 225 kHz <f< 590khz<="" td=""><td>100kHz<f< 200khz<="" td=""><td>K Factor = 13</td></f<></td></f<>     | 100kHz <f< 200khz<="" td=""><td>K Factor = 13</td></f<>  | K Factor = 13                 |

| 100  | 590 kHz <f< 1.5="" mhz<="" td=""><td>200kHz<f< 400khz<="" td=""><td>K Factor = 38</td></f<></td></f<> | 200kHz <f< 400khz<="" td=""><td>K Factor = 38</td></f<>  | K Factor = 38                 |

| 101  | 1.5 MHz <f< 4.0="" mhz<="" td=""><td>400kHz<f< 800khz<="" td=""><td>K Factor =100</td></f<></td></f<> | 400kHz <f< 800khz<="" td=""><td>K Factor =100</td></f<>  | K Factor =100                 |

| 110  | 4.0 MHz <f< 10="" mhz<="" td=""><td>800kHz<f< 1.6mhz<="" td=""><td>K Factor = 420</td></f<></td></f<> | 800kHz <f< 1.6mhz<="" td=""><td>K Factor = 420</td></f<> | K Factor = 420                |

| 111  | 10 MHz <f< td=""><td>1.6MHz<f< 3.2mhz<="" td=""><td>K Factor =1400</td></f<></td></f<>                | 1.6MHz <f< 3.2mhz<="" td=""><td>K Factor =1400</td></f<> | K Factor =1400                |

В режиме работы от кварцевого или керамического резонатора значение XFCN выбирается из таблицы.

В режиме работы от RC цепочки значение частоты рассчитывается по формуле:

$$F=1.23(10^3)/(R*C)$$

,

R - подтягивающий резистор а kOm;

С - величина конденсатора в рF.

В режиме работы от конденсатора значение частоты рассчитывается по формуле:

$$F=KF/(C*VDD),$$

где F - частота в MHz;

С - величина конденсатора между XLAT1 и XLAT2 выводами в рF.

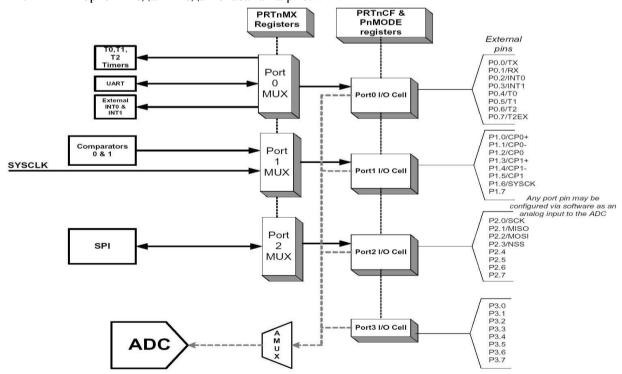

# 7.6.11. Особенности портов ввода/вывода

В микроконтроллерах семейства C8051F2xx отсутствует коммутатор внутренних ресурсов на внешние выводы Crossbar. Выводы всей внутренней цифровой периферии могут быть мультиплексированы только на строго определенные выводы портов. Функциональная схема соединения внутренней периферии к линиям портов ввода/вывода показана на рис.7.11.

Рис. 7.11. Функциональная схема разводки внутренней периферии на линии портов

7.6.12. PRT0MX - Регистр 0 мультиплексора портов ввода/вывода

| Hазвание регистра: PRT0MX - Port I/O MUX |       |       |       |            | K Register 0 |        |                  |        |  |

|------------------------------------------|-------|-------|-------|------------|--------------|--------|------------------|--------|--|

| SFR адрес / страница:                    |       | 0xE1  |       | Значение п | осле сброса: | 000000 | 00000000b (0x00) |        |  |

|                                          |       |       |       |            |              |        |                  |        |  |

|                                          | R/W   | R/W   | R/W   | R/W        | R/W          | R/W    | R                | R/W    |  |

|                                          | T2EXE | T2E   | T1E   | T0E        | INT1E        | INT0E  | -                | UARTEN |  |

|                                          | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3        | Bit 2  | Bit 1            | Bit 0  |  |

- Бит 7: T2EXE T2EX Enable Bit бит разрешения (1) разводки внешнего входа таймера 2 на соответствующий порт;

- Бит 6: T2E T2 Enable Bit бит разрешения (1) разводки выхода таймера 2 на соответствующий порт;

- Бит 5: T1E T1 Enable Bit бит разрешения (1) разводки выхода таймера 1 на соответствующий порт;

- Бит 4: T0E T0 Enable Bit бит разрешения (1) разводки выхода таймера 0 на соответствующий порт;

- Бит 3: INT1E INT1/ Enable Bit бит разрешения (1) разводки входа внешнего прерывания 1 на соответствующий порт;

- Бит 2: INT0E INT0/ Enable Bit бит разрешения (1) разводки входа внешнего прерывания 0 на соответствующий порт;

- Бит 1: зарезервирован;

- Бит 0: UARTEN UART0 Enable Bit бит разрешения (1) разводки сигналов UART0 на соответствующий порт.

7.6.13. PRT1MX - Регистр 1 мультиплексора портов ввода/вывода

| Название регистра:    |       |        | PRT1MX - P | ort I/O MUX | Register 1  |            |                  |        |   |

|-----------------------|-------|--------|------------|-------------|-------------|------------|------------------|--------|---|

| SFR адрес / страница: |       | 0xE2   |            | Значение п  | юсле сброса | ı: 0000000 | 00000000b (0x00) |        |   |

|                       |       |        |            |             |             |            |                  |        |   |

|                       | R     | R/W    | R          | R           | R           | R          | R/W              | R/W    | _ |

|                       | -     | SYSCKE | -          | 1           | -           | -          | CP10EN           | CP00EN |   |

|                       | Bit 7 | Bit 6  | Bit 5      | Bit 4       | Bit 3       | Bit 2      | Bit 1            | Bit 0  | = |

Бит 7: зарезервирован;

- Бит 6: SYSCKE SYSCLK Enable Bit бит разрешения (1) разводки выхода тактового генератора на соответствующий порт;

- Биты 5-2: зарезервированы;

- Бит 1: CP1OEN Comparator 1 Output Enable Bit бит разрешения (1) разводки выхода компаратора 1 на соответствующий порт;

- Бит 0: CPOOEN Comparator 0 Output Enable Bit бит разрешения (1) разводки выхода компаратора 0 на соответствующий порт.

7.6.14. PRT2MX - Регистр 2 мультиплексора портов ввода/вывода

| Название регистра:    |       |        | PRT2MX - Port I/O MUX Register 2 |                        |        |        |                  |         |  |

|-----------------------|-------|--------|----------------------------------|------------------------|--------|--------|------------------|---------|--|

| SFR адрес / страница: |       | 0xE3   |                                  | Значение после сброса: |        | 000000 | 00000000b (0x00) |         |  |

|                       |       |        |                                  | _                      | _      |        |                  | _       |  |

|                       | R     | R/W    | R                                | R                      | R      | R      | R/W              | R/W     |  |

|                       | GWPUD | P3WPUD | P2WPUD                           | P1WPUD                 | P0WPUD | -      | -                | SPI00EN |  |

|                       | Bit 7 | Bit 6  | Bit 5                            | Bit 4                  | Bit 3  | Bit 2  | Bit 1            | Bit 0   |  |

- Бит 7: GWPUD Global Port I/O Weak Pull-up Disable Bit бит общего запрещения "подтяжек" выводов портов ввода/вывода:

- 0 "подтяжки" разрешены (определяются битами PnWPUD);

- 1 "подтяжки" запрещены, значения битов PnWPUD игнорируются;

- Биты 6-3: PnWPUD Port n Weak Pull-up Disable Bits биты индивидуального запрещения "подтяжек" выводов портов:

- 0 "подтяжки" разрешены для порта п;

- 1 "подтяжки" запрещены для порта n;

- Биты 2-1 зарезервированы;

- Бит 0: SPIOOEN SPI Bus I/O Enable Bit бит разрешения разводки шины SPI на порт 2.

#### Название регистра: PnMODE - Port n Digital/Analog Input Mode P0MODE 0xF1 11111111b (0xFF) SFR адрес / страница: Значение после сброса: P1MODE 0xF2 P2MODE 0xF3 P3MODE 0xF4 R/W R/W R/W R/W R/W R/W R/W R/W Bit 7 Bit 5

7.6.15. PnMODE - Регистр порта п режима аналоговых/цифровых входов

Запись 0 в соответствующий бит порта запрещает режим цифрового ввода (переводит бит в режим аналогового ввода):

Bit 3

Bit 2

Bit 1

Bit 0

Запись 1 в соответствующий бит порта переводит линию порта в режим цифрового ввода.

Bit 4

#### 7.7. Достоинства и недостатки семейства C8051F2xx

Bit 6

Семейство микроконтроллеров C8051F2xx насчитывает 7 микроконтроллеров. Все они работают на частотах до 25 MHz, обеспечивая при этом производительность до 25MIPS. Архитектура этого семейства не похожа ни на одно из ранее описанных семейств.

Аналоговая периферия семейства рассчитана на использование в многоканальных систем сбора аналоговых данных. Ряд микроконтроллеров имеют до 32 входных каналов первого аналого-цифрового преобразователя. Другой особенностью является то, что входы аналоговых узлов не имеют самостоятельные выводы корпуса и могут быть настроены на любой из выводов портов ввода/вывода, что естественно усложнило коммутатор ресурсов Crossbar и начальную настройку портов микроконтроллера. Цифро-аналоговых преобразователей в этом семействе нет.

Цифровая периферия имеет все узлы стандартного микроконтроллера 8052, а также программируемый счетчик массив, расширенный обработчик прерываний, охранный таймер и монитор питания, а также встроенный программируемый генератор. В набор встроенных аппаратных интерфейсов входят: SMBus (совместимый с I2C) и по одному интерфейсу SPI и UART. Все интерфейсы поддерживают многопроцессорный режим. Кроме того, имеется развитый контроллер прерываний, обрабатывающий более 20 источников прерываний.

Семейство имеет встроенную Flash память среднего объема - 8K, что позволяет разместить в ней программы средней сложности. Некоторые из представителей семейства кроме стандартной памяти в 256 байт имеют еще 1К оперативной памяти, расположенной в адресном пространстве внешней памяти.

Стоимость микроконтроллеров этого семейства достаточно низка и составляет от \$7 до \$15. Это является безусловным достоинством семейства.

Перечисленные достоинства делают это семейство перспективным как для ряда специфических задач многоканальных систем измерения. Кроме того, низкая стоимость микроконтроллеров, не содержащих аналого-цифровые преобразователь (\$7-\$9), в сочетание с высокой производительностью и широким набором периферийных устройств, позволяют использовать их при решении широкого круга задач, не требующих наличия аналоговых подсистем.